1) What is the required baud rate for an efficient operation of serial port devices in 8051 microcontroller?

a. 1200

b. 2400

c. 4800

d. 9600

|

Answer

Explanation

|

ANSWER: 9600

Explanation:

No explanation is available for this question!

|

|

2) Which bit/s play/s a significant role in the selection of a bank register of Program Status Word (PSW)?

a. RS1

b. RS0

c. Both a & b

d. None of the above

|

Answer

Explanation

|

ANSWER: Both a & b

Explanation:

No explanation is available for this question!

|

|

3) Which base-register is preferred for address calculation of a byte that is to be accessed from program memory by base-register plus register-indirect addressing mode?

a. DPTR

b. PSW

c. PCON

d. All of the above

|

Answer

Explanation

|

ANSWER: DPTR

Explanation:

No explanation is available for this question!

|

|

4) Which bit must be set in TCON register in order to start the 'Timer 0' while operating in 'Mode 0'?

a. TR0

b. TF0

c. IT0

d. IE0

|

Answer

Explanation

|

ANSWER: TR0

Explanation:

No explanation is available for this question!

|

|

5) How many registers can be utilized to write the programs by an effective selection of register bank in program status word (PSW)?

a. 8

b. 16

c. 32

d. 64

|

Answer

Explanation

|

ANSWER: 32

Explanation:

No explanation is available for this question!

|

|

6) Which pin in the shift register mode (Mode 0) of serial communication allow the data transmission as well as reception?

a. TXD

b. RXD

c. RB8

d. REN

|

Answer

Explanation

|

ANSWER: RXD

Explanation:

No explanation is available for this question!

|

|

7) Which bits of opcode specify the type of registers to be used in the register addressing mode?

a. LSB

b. MSB

c. Both a & b

d. None of the above

|

Answer

Explanation

|

ANSWER: LSB

Explanation:

No explanation is available for this question!

|

|

8) Which instructions contribute to an effective adoption or utilization of stack memory which usually plays a crucial role in storage of intermediate results?

a. ACALL

b. RETI

c. PUSH & POP

d. All of the above

|

Answer

Explanation

|

ANSWER: All of the above

Explanation:

No explanation is available for this question!

|

|

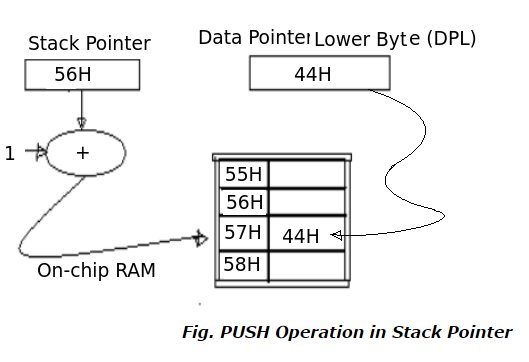

9) What does the following pictorial representation of PUSH operation in the stack pointer indicate among the below stated conclusions/inferences?

a. Stack Pointer is incremented by 2

b. Location 55H in on-chip stack memory gets loaded with 44H

c. Stack Pointer gets initialized by 56H

d. Data Pointer gets loaded with an immediate data 44H which ultimately leads to initialization of stack pointer

a. Only A

b. Only B

c. B & D

d. C & D

|

Answer

Explanation

|

ANSWER: C & D

Explanation:

No explanation is available for this question!

|

|

10) What is the status of stack pointer for the execution of PUSH and POP operations?

a. It gets post-decremented for PUSH & pre-incremented for POP

b. It gets pre-incremented for PUSH & post-decremented for POP

c. It gets pre-incremented for PUSH as well as POP

d. It gets post-decremented for PUSH as well as POP

|

Answer

Explanation

|

ANSWER: It gets pre-incremented for PUSH & post-decremented for POP

Explanation:

No explanation is available for this question!

|

|